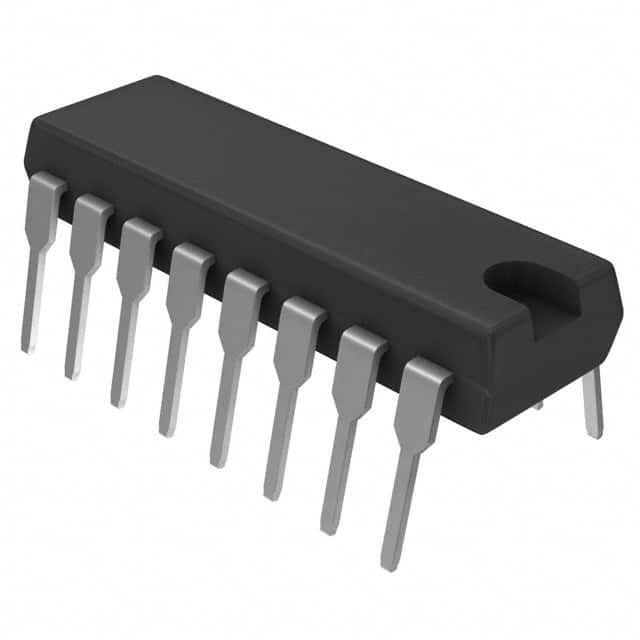

CD74HC173E

Product Overview

- Category: Integrated Circuit

- Use: Data Storage and Retrieval

- Characteristics: High-Speed, Quad D-Type Flip-Flop

- Package: 16-Pin DIP (Dual In-Line Package)

- Essence: Logic IC for storing and transferring digital data

- Packaging/Quantity: Available in tubes or reels, quantity varies based on supplier

Specifications

- Supply Voltage Range: 2V to 6V

- High-Level Input Voltage: 2V to VCC

- Low-Level Input Voltage: GND to 0.8V

- High-Level Output Current: -4mA

- Low-Level Output Current: 4mA

- Operating Temperature Range: -55°C to +125°C

Detailed Pin Configuration

- CP (Clock Pulse) Input

- D (Data) Inputs (D0-D3)

- Q (Flip-Flop Outputs) (Q0-Q3)

- GND (Ground)

- D (Data) Inputs (D4-D7)

- Q (Flip-Flop Outputs) (Q4-Q7)

- MR (Master Reset) Input

- VCC (Positive Power Supply)

Functional Features

- Quad D-Type Flip-Flop with Master Reset

- Synchronous Operation with Common Clock

- Positive-Edge Triggered Flip-Flops

- Direct Clear Input for Master Reset

- High-Speed Operation

- Wide Operating Voltage Range

- Balanced Propagation Delay and Transition Times

Advantages

- Compact and versatile integrated circuit

- High-speed operation allows for efficient data storage and retrieval

- Wide operating voltage range provides flexibility in various applications

- Balanced propagation delay and transition times ensure reliable performance

Disadvantages

- Limited number of flip-flops (8 in total)

- Requires external clock signal for synchronous operation

- Not suitable for applications requiring a large number of storage elements

Working Principles

The CD74HC173E is a quad D-type flip-flop with master reset. It operates synchronously with a common clock signal, which triggers the positive-edge triggered flip-flops. The data inputs (D0-D7) are stored and transferred to the corresponding flip-flop outputs (Q0-Q7) based on the clock pulse. The master reset input (MR) allows for clearing all flip-flops simultaneously.

Detailed Application Field Plans

The CD74HC173E can be used in various applications that require data storage and retrieval. Some potential application fields include:

- Digital Communication Systems: Used for buffering and synchronization of digital signals.

- Microcontroller Interfacing: Enables efficient data transfer between microcontrollers and external devices.

- Memory Addressing: Can be utilized for address decoding in memory systems.

- Data Processing Units: Facilitates temporary storage of intermediate results during complex calculations.

Detailed and Complete Alternative Models

- SN74HC173N: Similar quad D-type flip-flop with master reset, offered by Texas Instruments.

- MC74HC173AN: Equivalent IC manufactured by ON Semiconductor.

- 74HCT173: High-speed CMOS logic IC with similar functionality, available from multiple suppliers.

Please note that the above list is not exhaustive, and there may be other alternative models available in the market.

Word count: 409 words

רשום 10 שאלות ותשובות נפוצות הקשורות ליישום של CD74HC173E בפתרונות טכניים

Question: What is the function of CD74HC173E?

Answer: CD74HC173E is a high-speed CMOS device that functions as a 4-bit D-type register with 3-state outputs.Question: What are the typical applications of CD74HC173E?

Answer: CD74HC173E is commonly used in microprocessor systems, memory address registers, and other digital systems.Question: What is the operating voltage range for CD74HC173E?

Answer: The operating voltage range for CD74HC173E is 2V to 6V.Question: Can CD74HC173E be cascaded for larger register applications?

Answer: Yes, CD74HC173E can be easily cascaded to create larger register applications.Question: What is the maximum clock frequency for CD74HC173E?

Answer: The maximum clock frequency for CD74HC173E is typically around 25MHz.Question: Does CD74HC173E have built-in output enable functionality?

Answer: Yes, CD74HC173E features a 3-state output with a built-in output enable function.Question: What is the power dissipation of CD74HC173E?

Answer: The power dissipation of CD74HC173E is typically low, making it suitable for power-sensitive applications.Question: Is CD74HC173E compatible with TTL inputs?

Answer: Yes, CD74HC173E is compatible with TTL inputs, providing versatile interfacing capabilities.Question: Can CD74HC173E withstand electrostatic discharge (ESD)?

Answer: CD74HC173E is designed to withstand ESD up to 2000V, making it robust in real-world environments.Question: Are there any specific layout considerations for using CD74HC173E in PCB designs?

Answer: It is recommended to follow standard high-speed CMOS layout guidelines to optimize performance when using CD74HC173E in PCB designs.